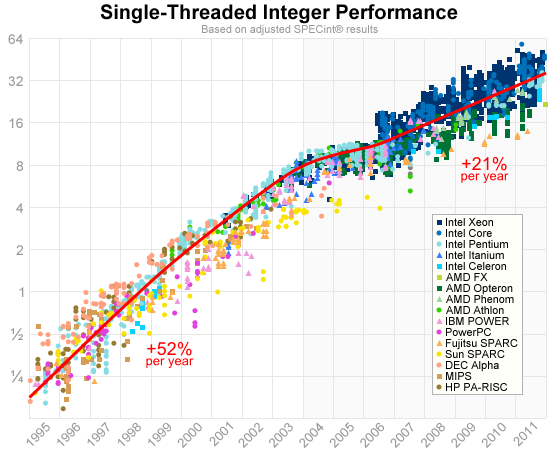

The final ISA showdown: Is ARM, x86, or MIPS intrinsically more power efficient? - Architectures and Processors blog - Arm Community blogs - Arm Community

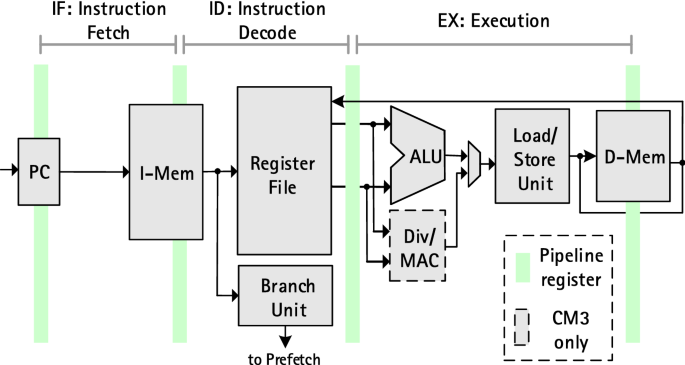

cpu architecture - How can I implement the instruction jrlti (jump-register if less than immediate) in the MIPS one cycle datapath? - Stack Overflow

GitHub - bveyseloglu/Single-and-Multi-Cycle-MIPS-CPU-Design: A very simple single cycle and multi cycle MIPS CPU design written in VHDL. The design explained in detail.

MIPS-Core Application Specific Instruction-Set Processor for IDEA Cryptography - Comparison between Single-Cycle and Multi-Cycle Architectures | DeepAI

How well is your mainframe outsourcer managing capacity and performance? - Part 2 - Understanding MIPS and MSU - SMT Data

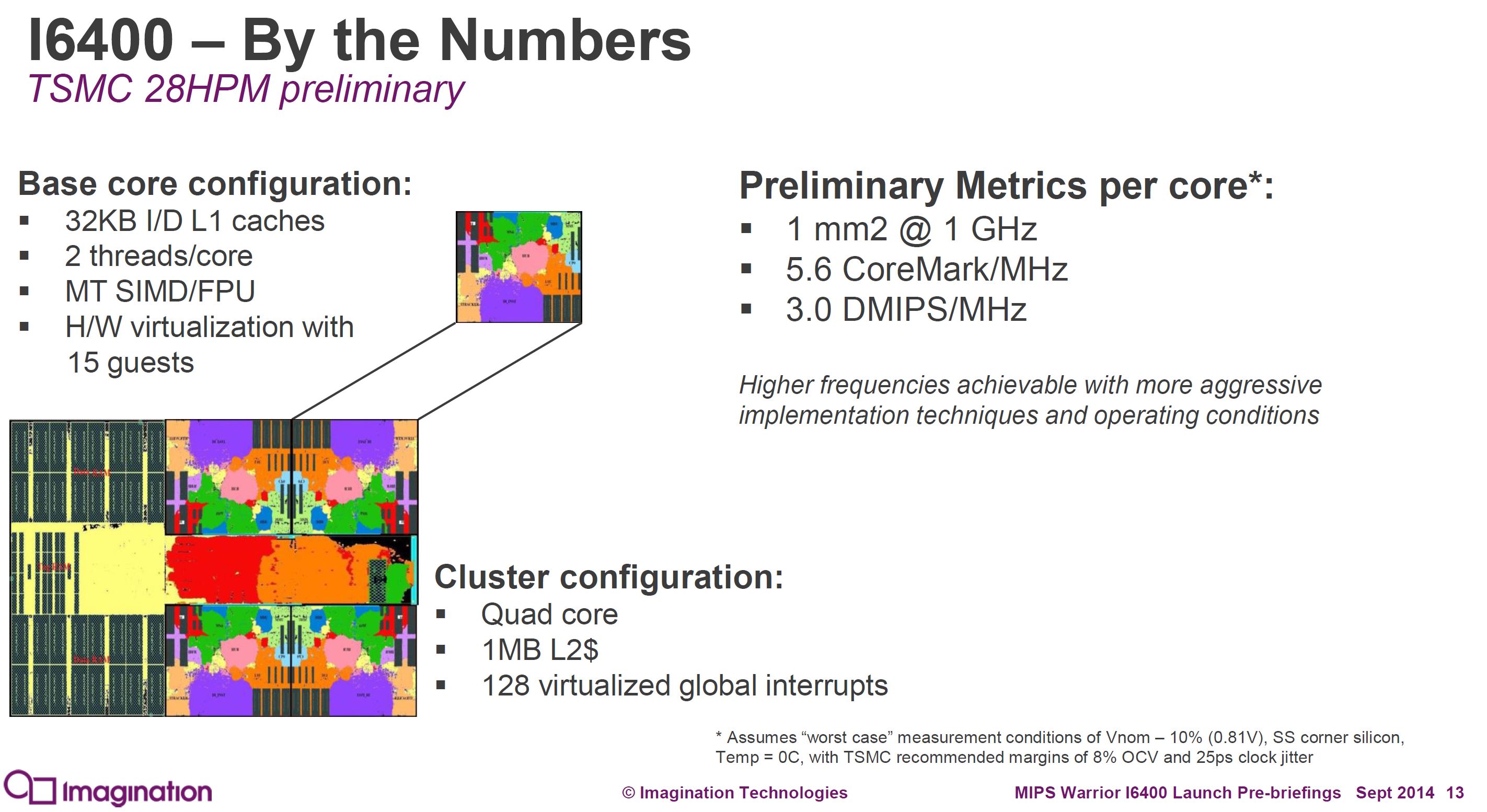

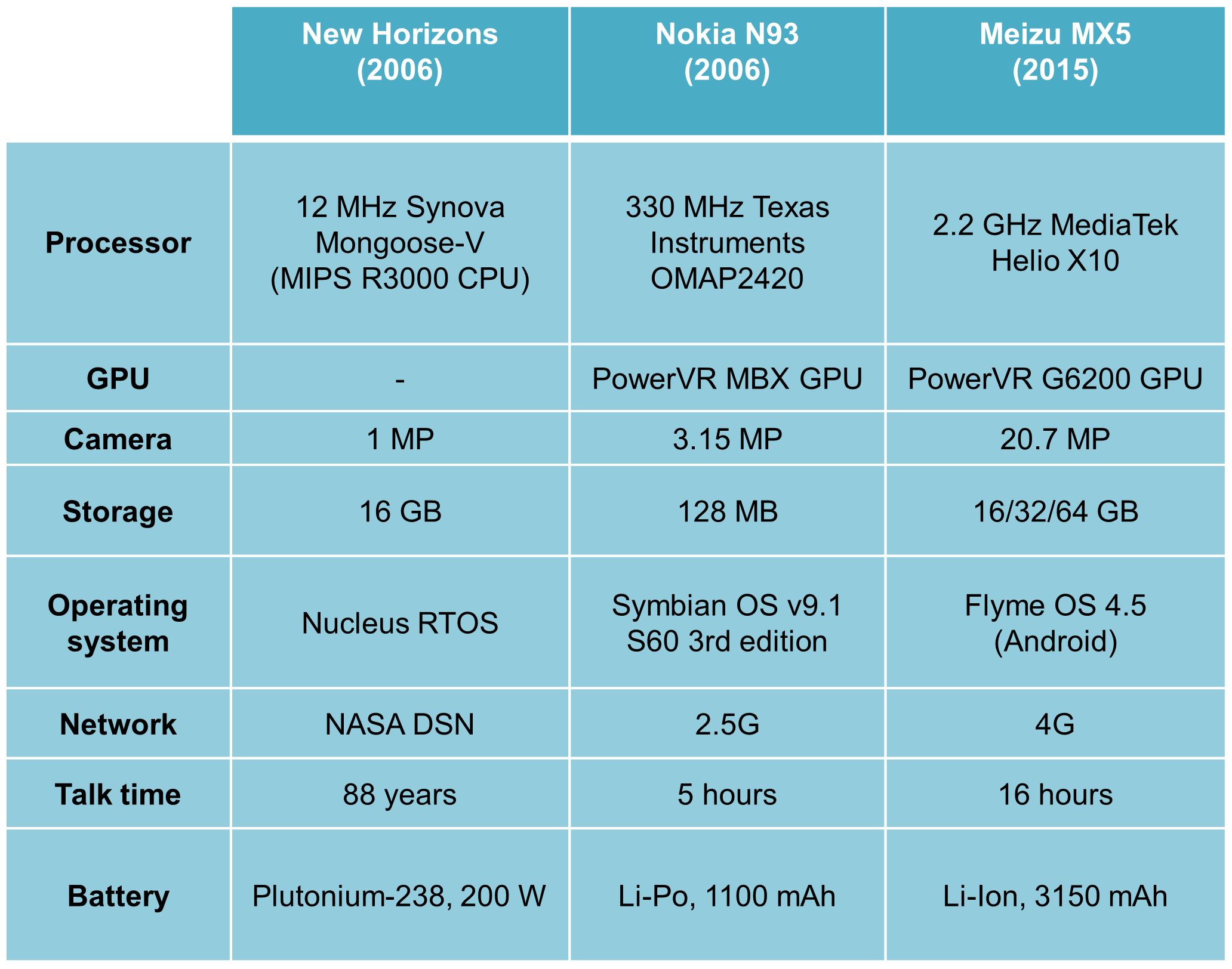

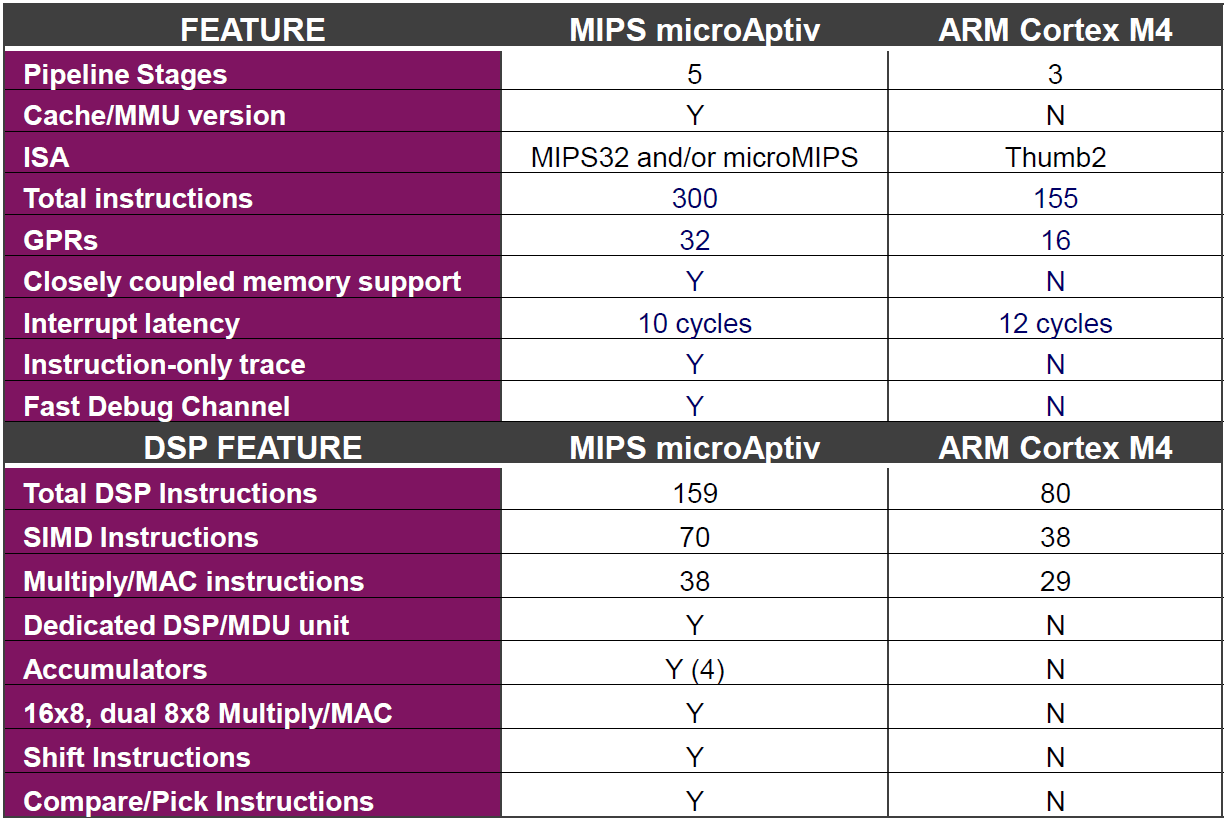

interAptiv and microAptiv Architectures - MIPS Technologies Updates Processor IP Lineup with Aptiv Series