![PDF] An analytical equation for the oscillation frequency of high-frequency ring oscillators | Semantic Scholar PDF] An analytical equation for the oscillation frequency of high-frequency ring oscillators | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/f0ecec5fb0ea9248851dea72cc4da586e36e25fa/2-Figure1-1.png)

PDF] An analytical equation for the oscillation frequency of high-frequency ring oscillators | Semantic Scholar

PDF) DESIGN OF VCO USING CURRENT MODE LOGIC WITH LOW SUPPLY SENSITIVITY | Editor IJRET - Academia.edu

Analysis and Comparison of Ring and LC-Tank Oscillators for 65 nm Integration of Rad-Hard VCO for SpaceFibre Applications | SpringerLink

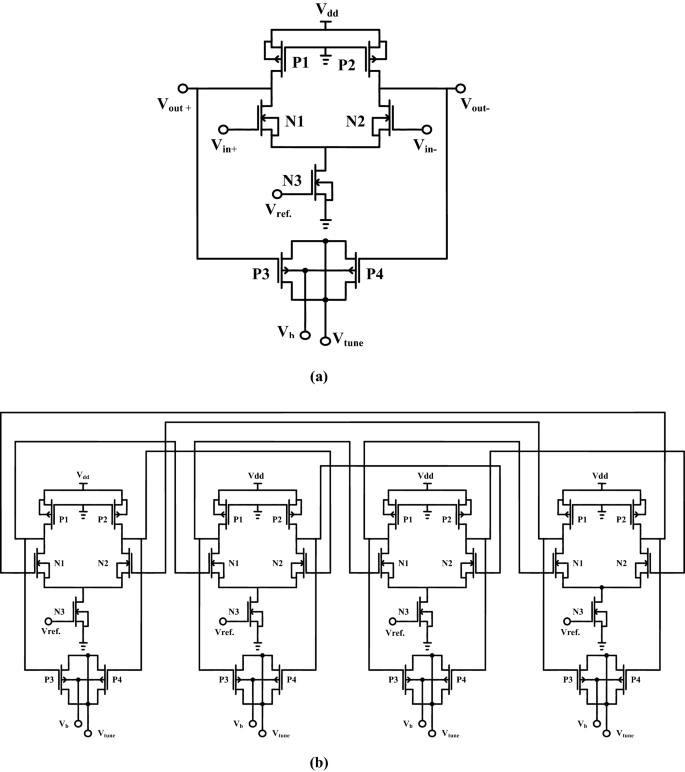

3-stage CML ring-VCO circuit diagram (W1=10 µm, W2 = 8 µm, W3 = 100 µm,... | Download Scientific Diagram

Self-Timed Rings: A Promising Solution for Generating High-Speed High Resolution Low-Phase Noise Clocks

![PDF] Oscillation frequency in CML and ESCL ring oscillators | Semantic Scholar PDF] Oscillation frequency in CML and ESCL ring oscillators | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/34b00687dda121f8c253111899fe5d08784926e8/2-Figure2-1.png)